# SC16C850L

1.8 V single UART, 5 Mbit/s (max.) with 128-byte FIFOs, infrared (IrDA) and 16 mode or 68 mode parallel bus interface

Rev. 04 — 13 December 2007

**Product data sheet**

## 1. General description

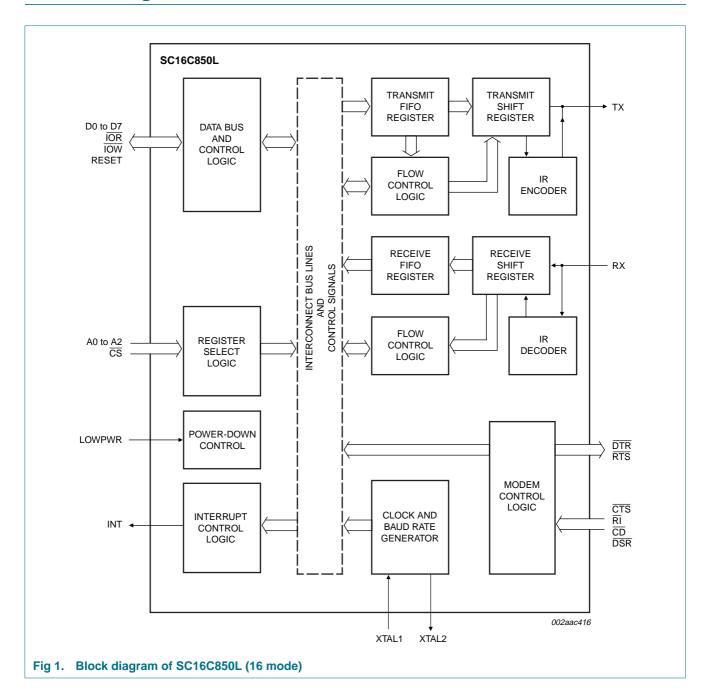

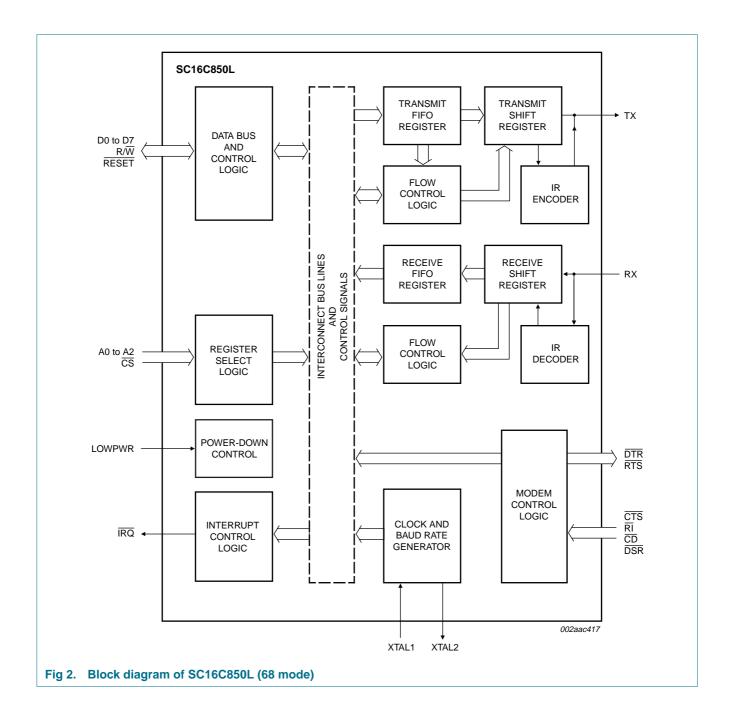

The SC16C850L is a 1.8 V, low power, single channel Universal Asynchronous Receiver and Transmitter (UART) used for serial data communications. Its principal function is to convert parallel data into serial data and vice versa. The UART can handle serial data rates up to 5 Mbit/s. The SC16C850L is functionally (software) compatible with the SC16C650B. SC16C850L can be programmed to operate in extended mode (see Section 6.2) where additional advanced UART features are available. The SC16C850L UART provides enhanced UART functions with 128-byte FIFOs, modem control interface, and IrDA encoder/decoder. On-board status registers provide the user with error indications and operational status. System interrupts and modem control features may be tailored by software to meet specific user requirements. An internal loopback capability allows on-board diagnostics.

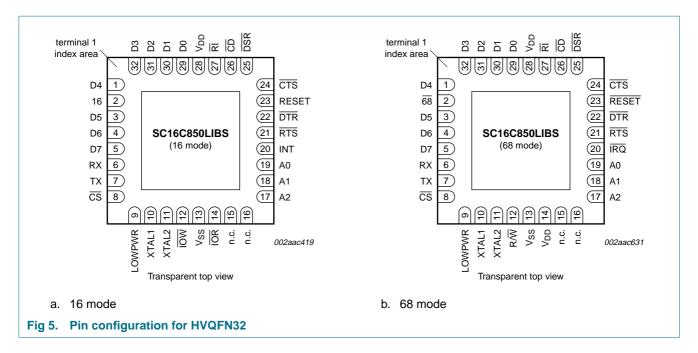

The SC16C850LIBS with Intel (16 mode) or Motorola (68 mode) bus host interface operates at 1.8 V and is available in a very small (Micro-UART) HVQFN32 package.

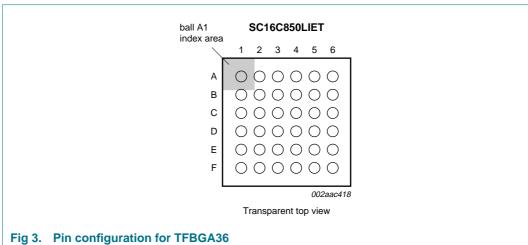

The SC16C850LIET with Intel (16 mode) bus host interface operates at 1.8 V and is available in a very small TFBGA36 package.

#### 2. Features

- Single channel high performance UART

- Intel or Motorola bus interface selectable using 16/68 pin

- 1.8 V operation

- Up to 5 Mbit/s data rate

- 128-byte transmit FIFO to reduce the bandwidth requirement of the external CPU

- 128-byte receive FIFO with error flags to reduce the bandwidth requirement of the external CPU

- 128 programmable Receive and Transmit FIFO interrupt trigger levels

- 128 Receive and Transmit FIFO reporting levels (level counters)

- Automatic software (Xon/Xoff) and hardware (RTS/CTS or DTR/DSR) flow control

- Industrial temperature range (-40 °C to +85 °C)

- 128 hardware and software trigger levels

- Automatic 9-bit mode (RS-485) address detection

- Automatic RS-485 driver turn-around with programmable delay

- UART software reset

- High resolution clock prescaler, from 0 to 15 with granularity of <sup>1</sup>/<sub>16</sub> to allow non-standard UART clock to be used

- Programmable Xon/Xoff characters

## 1.8 V single UART with 128-byte FIFOs and IrDA encoder/decoder

- Software selectable baud rate generator

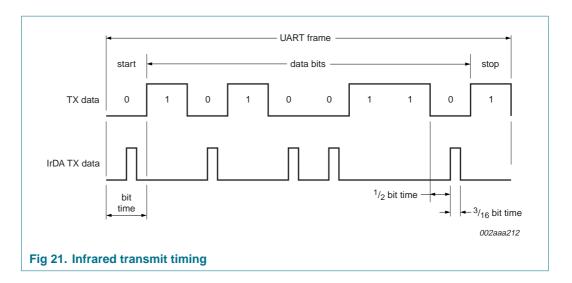

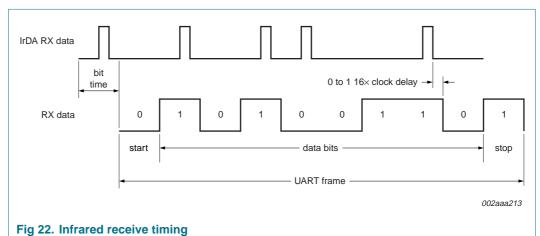

- Support IrDA version 1.0 (up to 115.2 kbit/s)

- Standard modem interface or infrared IrDA encoder/decoder interface

- Enhanced Sleep mode and low power feature

- Modem control functions (CTS, RTS, DSR, DTR, RI, CD)

- Independent transmitter and receiver enable/disable

- Pb-free, RoHS compliant package offered

# 3. Ordering information

## Table 1. Ordering information

| Type number  | Package |                                                                                                            |          |  |  |  |  |

|--------------|---------|------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|

|              | Name    | Description                                                                                                | Version  |  |  |  |  |

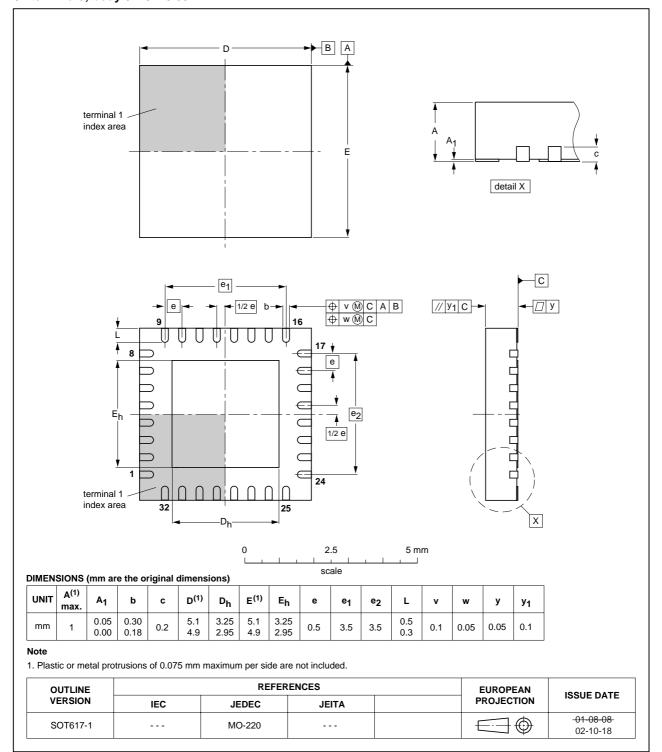

| SC16C850LIBS | HVQFN32 | plastic thermal enhanced very thin quad flat package; no leads; 32 terminals; body $5\times5\times0.85$ mm | SOT617-1 |  |  |  |  |

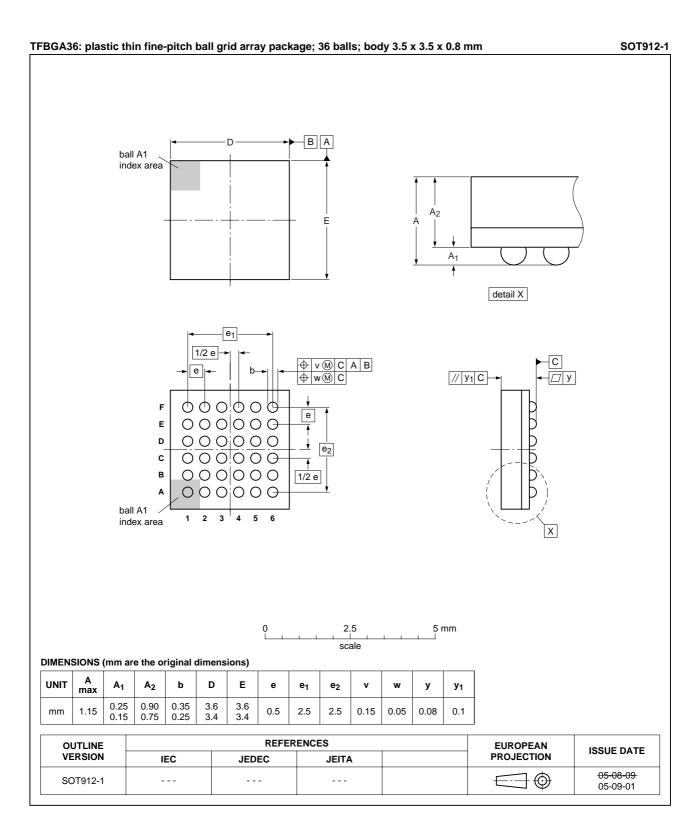

| SC16C850LIET | TFBGA36 | plastic thin fine-pitch ball grid array package; 36 balls; body $3.5\times3.5\times0.8~\text{mm}$          | SOT912-1 |  |  |  |  |

## 1.8 V single UART with 128-byte FIFOs and IrDA encoder/decoder

# 4. Block diagram

## 1.8 V single UART with 128-byte FIFOs and IrDA encoder/decoder

SC16C850L **NXP Semiconductors**

1.8 V single UART with 128-byte FIFOs and IrDA encoder/decoder

# **Pinning information**

## 5.1 Pinning

002aac421

Transparent top view.

Fig 4. Ball mapping for TFBGA36

## 1.8 V single UART with 128-byte FIFOs and IrDA encoder/decoder

## 5.2 Pin description

Table 2. Pin description

| Symbol | Pin     |         | Туре | Description                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|--------|---------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|        | TFBGA36 | HVQFN32 |      |                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 16/68  | -       | 2       | I    | Bus select. Intel or Motorola bus select.                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|        |         |         |      | When $16/\overline{68}$ pin is at logic 1 or left unconnected (internally pulled-up) the device will operate in Intel bus (16 mode) type of interface.                                                                                                                                                                                                    |  |  |  |  |

|        |         |         |      | When $16/\overline{68}$ pin is at logic 0, the device will operate in Motorola bus (68 mode) type of interface.                                                                                                                                                                                                                                           |  |  |  |  |

| A0     | C1      | 19      | I    | Address 0 select bit. Internal register address selection.                                                                                                                                                                                                                                                                                                |  |  |  |  |

| A1     | C3      | 18      | I    | Address 1 select bit. Internal register address selection.                                                                                                                                                                                                                                                                                                |  |  |  |  |

| A2     | B1      | 17      | I    | Address 2 select bit. Internal register address selection.                                                                                                                                                                                                                                                                                                |  |  |  |  |

| CD     | E3      | 26      | I    | <b>Carrier Detect (active LOW).</b> A logic 0 on this pin indicates that a carrier has been detected by the modem. Status can be tested by reading MSR[7].                                                                                                                                                                                                |  |  |  |  |

| CS     | B6      | 8       | I    | <b>Chip Select (active LOW).</b> In 16 mode or 68 mode, this input is chip select for the UART.                                                                                                                                                                                                                                                           |  |  |  |  |

| CTS    | D3      | 24      | I    | Clear to Send (active LOW). A logic 0 on the $\overline{\text{CTS}}$ pin indicates the modem or data set is ready to accept transmit data from the SC16C850L. Status can be tested by reading MSR[4].                                                                                                                                                     |  |  |  |  |

| DSR    | F2      | 25      | I    | <b>Data Set Ready (active LOW).</b> A logic 0 on this pin indicates the modem or data set is powered-on and is ready for data exchange with the UART. Status can be tested by reading MSR[5].                                                                                                                                                             |  |  |  |  |

| DTR    | E1      | 22      | 0    | Data Terminal Ready (active LOW). A logic 0 on this pin indicates that the SC16C850L is powered-on and ready. This pin can be controlled via the modem control register. Writing a logic 1 to MCR[0] will set the $\overline{DTR}$ output to logic 0, enabling the modem. This pin will be a logic 1 after writing a logic 0 to MCR[0], or after a reset. |  |  |  |  |

## 1.8 V single UART with 128-byte FIFOs and IrDA encoder/decoder

Table 2.

Pin description ...continued

| Symbol             | •        |         | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|--------------------|----------|---------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Cymbol             | TFBGA36  | HVQFN32 | . ypc | 2000 piloti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| D0                 | F4       | 29      | I/O   | <b>Data bus (bidirectional).</b> These pins are the 8-bit, 3-state data bus for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| D1                 | E4       | 30      | I/O   | transferring information to or from the controlling CPU. D0 is the least                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| D2                 | F5       | 31      | I/O   | significant bit and the first data bit in a transmit or receive serial data stream.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| D3                 | E5       | 32      | I/O   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| D4                 | F6       | 1       | I/O   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| D5                 | E6       | 3       | I/O   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| D6                 | D6       | 4       | I/O   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| D7                 | D5       | 5       | I/O   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

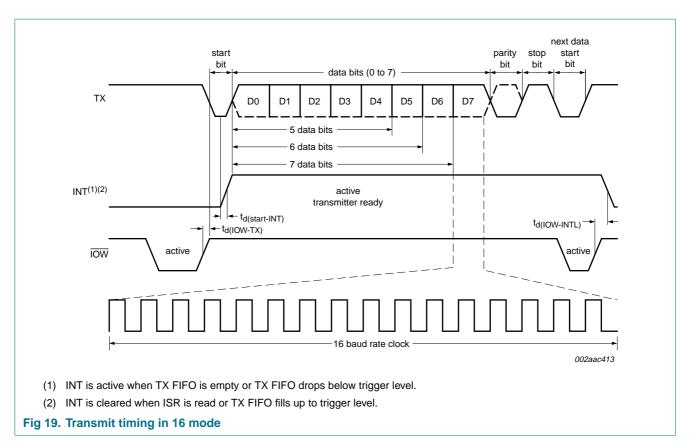

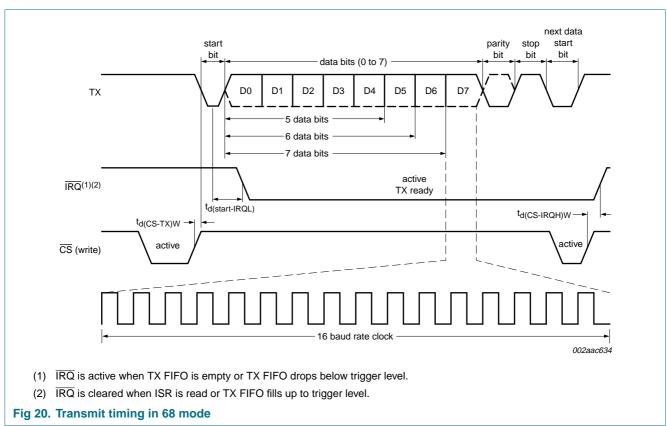

| INT<br>(IRQ)       | -        | 20      | 0     | When $16/\overline{68}$ pin is at logic 1 or unconnected, this output becomes active HIGH interrupt output. The output state is defined by the user through the software setting of MCR[5]. INT is set to the active mode when MCR[5] is set to a logic 1. INT is set to the open-source mode when MCR[5] is set to a logic 0. When $16/\overline{68}$ pin is at logic 0, this output becomes device interrupt output                                                                                                                                                                                 |  |  |  |

|                    |          |         |       | (active LOW, open-drain). An external pull-up resistor to V <sub>DD</sub> is required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| INT                | D1       | -       | 0     | Interrupt output (active HIGH). The output state is defined by the user through the software setting of MCR[5]. INT is set to the active mode when MCR[5] is set to a logic 1. INT is set to the open-source mode when MCR[5] is set to a logic 0.                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

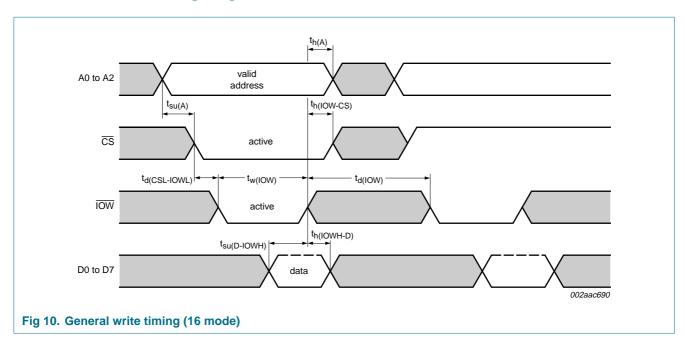

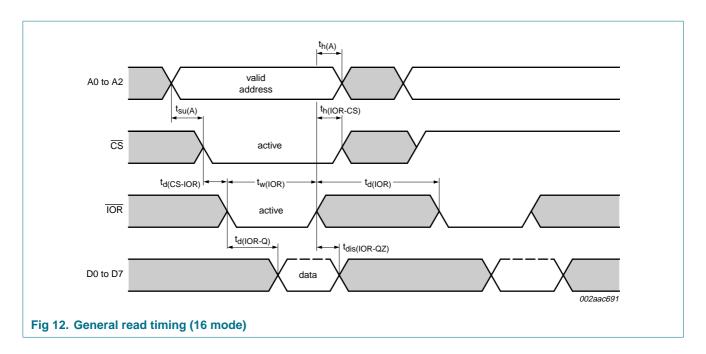

| ĪOR                | -        | 14      | I     | When $16\overline{/68}$ pin is at logic 1, this input becomes the read strobe (active LOW).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| (V <sub>DD</sub> ) |          |         |       | When $16/\overline{68}$ pin is at logic 0, this input pin is not used and should be connected to $V_{DD}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| ĪOR                | A3       | -       | I     | Read strobe (active LOW).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

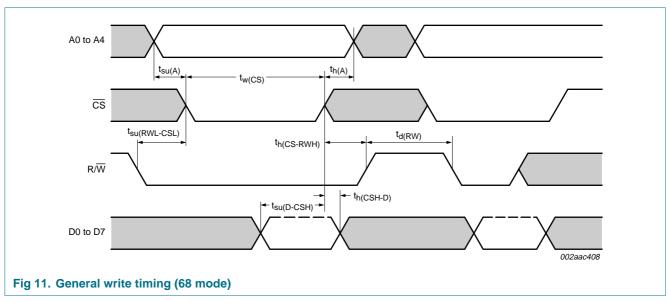

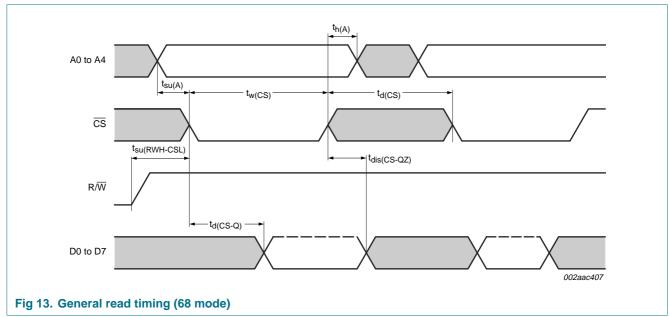

| IOW<br>(R/W)       | -        | 12      | I     | When $16\overline{/68}$ pin is at logic 1 or unconnected, this input becomes the write strobe (active LOW).  When $16\overline{/68}$ pin is at logic 0, this input becomes read strobe when it is at logic                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| ĪOW                | D4       |         | 1     | HIGH, and write strobe when it is at logic LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| LOWPWR             | B4<br>B5 | 9       | I     | Write strobe (active LOW).  Low Power. When asserted (active HIGH), the device immediately goes into low power mode. The oscillator is shut-off and some host interface pins are isolated from the host's bus to reduce power consumption. The device only returns to normal mode when the LOWPWR pin is de-asserted. On the negative edge of a de-asserting LOWPWR signal, the device is automatically reset and all registers return to their default reset states. This pin has an internal pull-down resistor, therefore, it can be left unconnected (refer to Section 6.12 "Low power feature"). |  |  |  |

| RESET<br>(RESET)   | -        | 23      | I     | Master Reset. When 16/68 pin is at logic 1 or unconnected, this input becomes the RESET pin (active HIGH).  When 16/68 pin is at logic LOW, this input pin becomes RESET (active LOW). (See Section 7.23 "SC16C850L external reset condition and software reset" for initialization details.)                                                                                                                                                                                                                                                                                                         |  |  |  |

| RESET              | F1       | -       | I     | Reset input (active HIGH). See Section 7.23 "SC16C850L external reset condition and software reset" for initialization details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| RI                 | F3       | 27      | I     | <b>Ring Indicator (active LOW).</b> A logic 0 on this pin indicates the modem has received a ringing signal from the telephone line. A logic 1 transition on this input pin will generate an interrupt if modem status interrupt is enabled. Status can be tested by reading MCR[6].                                                                                                                                                                                                                                                                                                                  |  |  |  |

## 1.8 V single UART with 128-byte FIFOs and IrDA encoder/decoder

Table 2.

Pin description ...continued

| Symbol          | Pin     |                     | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|-----------------|---------|---------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                 | TFBGA36 | HVQFN32             |      |                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| RTS             | D2      | 21                  | 0    | Request to Send (active LOW). A logic 0 on the RTS pin indicates the transmitter has data ready and waiting to send. Writing a logic 1 in the modem control register MCR[1] will set this pin to a logic 0, indicating data is available. After a reset this pin will be set to a logic 1.                                                                                                                  |  |  |  |  |

| RX              | C6      | 6                   | I    | <b>UART receive data.</b> The RX signal will be a logic 1 during reset, idle (no data), or when not receiving data. During the local loopback mode, the RX input pin is disabled and TX data is connected to the UART RX input, internally.                                                                                                                                                                 |  |  |  |  |

| TX              | C5      | 7                   | 0    | <b>UART transmit data.</b> The TX signal will be a logic 1 during reset, idle (no data), or when the transmitter is disabled. During the local loopback mode, the TX output pin is disabled and TX data is internally connected to the UART RX input.                                                                                                                                                       |  |  |  |  |

| $V_{DD}$        | A1, D4  | 28                  | I    | Power supply input.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| V <sub>SS</sub> | C2, C4  | 13 <mark>[1]</mark> | I    | Signal and power ground.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

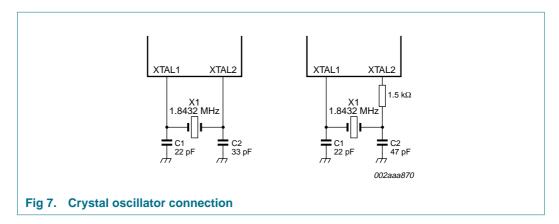

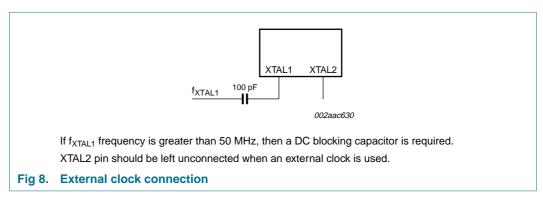

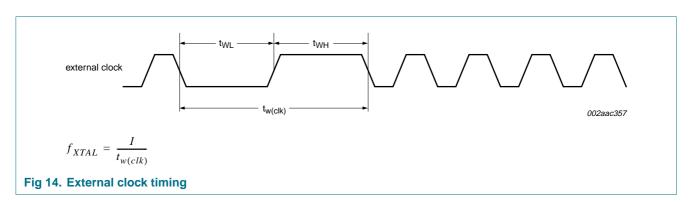

| XTAL1           | A6      | 10                  | I    | Crystal or external clock input. Functions as a crystal input or as an external clock input. A crystal can be connected between this pin and XTAL2 to form an internal oscillator circuit. Alternatively, an external clock can be connected to this pin to provide custom data rates (see <a href="Section 6.9">Section 6.9</a> "Programmable baud rate generator"). See <a href="Figure 8.">Figure 8.</a> |  |  |  |  |

| XTAL2           | A5      | 11                  | 0    | <b>Output of the crystal oscillator or buffered clock.</b> Crystal oscillator output or buffered clock output. Should be left open if an external clock is connected to XTAL1.                                                                                                                                                                                                                              |  |  |  |  |

<sup>[1]</sup> HVQFN package die supply ground is connected to both V<sub>SS</sub> pin and exposed center pad. V<sub>SS</sub> pin must be connected to supply ground for proper device operation. For enhanced thermal, electrical, and board level performance, the exposed pad needs to be soldered to the board using a corresponding thermal pad on the board and for proper heat conduction through the board, thermal vias need to be incorporated in the PCB in the thermal pad region.

#### 1.8 V single UART with 128-byte FIFOs and IrDA encoder/decoder

## 6. Functional description

The SC16C850L provides serial asynchronous receive data synchronization, parallel-to-serial and serial-to-parallel data conversions for both the transmitter and receiver sections. These functions are necessary for converting the serial data stream into parallel data that is required with digital data systems. Synchronization for the serial data stream is accomplished by adding start and stop bits to the transmit data to form a data character (character orientated protocol). Data integrity is ensured by attaching a parity bit to the data character. The parity bit is checked by the receiver for any transmission bit errors. The electronic circuitry to provide all these functions is fairly complex, especially when manufactured on a single integrated silicon chip. The SC16C850L represents such an integration with greatly enhanced features. The SC16C850L is fabricated with an advanced CMOS process.

The SC16C850L is an upward solution to the SC16C650B that provides a single UART capability with 128 bytes of transmit and receive FIFO memory, instead of 32 bytes for the 16C650B and 16 bytes in the 16C550B. The SC16C850L is designed to work with high speed modems and shared network environments that require fast data processing time. Increased performance is realized in the SC16C850L by the transmit and receive FIFOs. This allows the external processor to handle more networking tasks within a given time. In addition, the four selectable receive and transmit FIFO trigger interrupt levels are provided in 16C650 mode, or 128 programmable levels are provided in the extended mode for maximum data throughput performance especially when operating in a multi-channel environment (see Section 6.2 "Extended mode (128-byte FIFO)"). The FIFO memory greatly reduces the bandwidth requirement of the external controlling CPU and increases performance. A low power pin (LOWPWR) is provided to further reduce power consumption by isolating the host bus interface.

The SC16C850L is capable of operation up to 5 Mbit/s with an external 80 MHz clock. With a crystal, the SC16C850L is capable of operation up to 1.5 Mbit/s.

The rich feature set of the SC16C850L is available through internal registers. These features are: selectable and programmable receive and transmit FIFO trigger levels, selectable TX and RX baud rates, and modem interface controls, and are all standard features. Following a power-on reset, an external reset, or a software reset, the SC16C850L is software compatible with the previous generation, SC16C550B, and SC16C650B.

## 6.1 UART selection

The UART provides the user with the capability to bidirectionally transfer information between an external CPU, the SC16C850L package, and an external serial device. A logic 0 (LOW) on chip select pin  $\overline{\text{CS}}$  allows the user to configure, send data, and/or receive data via the UART. Refer to Table 3 and Table 4.

Table 3. Serial port selection (Intel interface) H = HIGH: L = LOW.

| Chip Select | Function    |

|-------------|-------------|

| CS = H      | none        |

| CS = L      | UART select |

## 1.8 V single UART with 128-byte FIFOs and IrDA encoder/decoder

Table 4. Serial port selection (Motorola interface)

H = HIGH; L = LOW.

| Chip Select         | Function    |

|---------------------|-------------|

| $\overline{CS} = H$ | none        |

| CS = L              | UART select |

## 6.2 Extended mode (128-byte FIFO)

The device is in the extended mode when any of these four registers contains any value other than 0: FLWCNTH, FLWCNTL, TXINTLVL, RXINTLVL.

## 6.3 Internal registers

The SC16C850L provides a set of 25 internal registers for monitoring and controlling the functions of the UART. These registers are shown in Table 5.

Table 5. Internal registers decoding

| A2   | <b>A</b> 1 | Α0      | Read mode                              | Write mode                            |

|------|------------|---------|----------------------------------------|---------------------------------------|

| Gen  | eral r     | egiste  | er set (THR/RHR, IER/ISR, MCR/MSR, I   | FCR, LSR, SPR)[1]                     |

| 0    | 0          | 0       | Receive Holding Register               | Transmit Holding Register             |

| 0    | 0          | 1       | Interrupt Enable Register              | Interrupt Enable Register             |

| 0    | 1          | 0       | Interrupt Status Register              | FIFO Control Register                 |

| 0    | 1          | 1       | Line Control Register                  | Line Control Register                 |

| 1    | 0          | 0       | Modem Control Register                 | Modem Control Register                |

| 1    | 0          | 1       | Line Status Register                   | Extra Feature Control Register (EFCR) |

| 1    | 1          | 0       | Modem Status Register                  | n/a                                   |

| 1    | 1          | 1       | Scratchpad Register                    | Scratchpad Register                   |

| Bau  | d rate     | regis   | iter set (DLL/DLM)[2]                  |                                       |

| 0    | 0          | 0       | LSB of Divisor Latch                   | LSB of Divisor Latch                  |

| 0    | 0          | 1       | MSB of Divisor Latch                   | MSB of Divisor Latch                  |

| Sec  | ond s      | pecia   | l register set (TXLVLCNT/RXLVLCNT)     | [3]                                   |

| 0    | 1          | 1       | Transmit FIFO Level Count              | n/a                                   |

| 1    | 0          | 0       | Receive FIFO Level Count               | n/a                                   |

| Enh  | anced      | d featu | ure register set (EFR, Xon1/Xon2, Xoff | f1/Xoff2)[ <u>4]</u>                  |

| 0    | 1          | 0       | Enhanced Feature Register              | Enhanced Feature Register             |

| 1    | 0          | 0       | Xon1 word                              | Xon1 word                             |

| 1    | 0          | 1       | Xon2 word                              | Xon2 word                             |

| 1    | 1          | 0       | Xoff1 word                             | Xoff1 word                            |

| 1    | 1          | 1       | Xoff2 word                             | Xoff2 word                            |

| Firs | t extra    | a featı | ure register set (TXINTLVL/RXINTLVL,   | FLWCNTH/FLWCNTL)[5]                   |

| 0    | 1          | 0       | Transmit FIFO Interrupt Level          | Transmit FIFO Interrupt Level         |

| 1    | 0          | 0       | Receive FIFO Interrupt Level           | Receive FIFO Interrupt Level          |

| 1    | 1          | 0       | Flow Control Count High                | Flow Control Count High               |

| 1    | 1          | 1       | Flow Control Count Low                 | Flow Control Count Low                |

### 1.8 V single UART with 128-byte FIFOs and IrDA encoder/decoder

Table 5. Internal registers decoding ...continued

| A2                                                                      | <b>A</b> 1 | Α0 | Read mode                             | Write mode                            |  |  |

|-------------------------------------------------------------------------|------------|----|---------------------------------------|---------------------------------------|--|--|

| Second extra feature register set (CLKPRES, RS485TIME, AFCR2, AFCR1)[6] |            |    |                                       |                                       |  |  |

| 0                                                                       | 1          | 0  | Clock Prescaler                       | Clock Prescaler                       |  |  |

| 1                                                                       | 0          | 0  | RS-485 turn-around Timer              | RS-485 turn-around Timer              |  |  |

| 1                                                                       | 1          | 0  | Additional Feature Control Register 2 | Additional Feature Control Register 2 |  |  |

| 1                                                                       | 1          | 1  | Additional Feature Control Register 1 | Additional Feature Control Register 1 |  |  |

- [1] These registers are accessible only when LCR[7] is a logic 0.

- [2] These registers are accessible only when LCR[7] is a logic 1.

- [3] Second Special registers are accessible only when EFCR[0] = 1.

- [4] Enhanced Feature Registers are only accessible when LCR = 0xBF.

- [5] First Extra Feature Registers are only accessible when EFCR[2:1] = 01b.

- [6] Second Extra Feature Registers are only accessible when EFCR[2:1] = 10b.

## 6.4 FIFO operation

### 6.4.1 32-byte FIFO mode

When all four of these registers (TXINTLVL, RXINTLVL, FLWCNTH, FLWCNTL) in the 'first extra feature register set' are empty (0x00) the transmit and receive trigger levels are set by FCR[7:4]. In this mode the transmit and receive trigger levels are backward compatible to the SC16C650B (see <u>Table 6</u>), and the FIFO sizes are 32 entries. The transmit and receive data FIFOs are enabled by the FIFO Control Register bit 0 (FCR[0]). It should be noted that the user can set the transmit trigger levels by writing to the FCR, but activation will not take place until EFR[4] is set to a logic 1. The receiver FIFO section includes a time-out function to ensure data is delivered to the external CPU (see Section 6.8). Please refer to <u>Table 11</u> and <u>Table 12</u> for the setting of FCR[7:4].

Table 6. Interrupt trigger level and flow control mechanism

| FCR[7:6] | FCR[5:4] | INT pin activa | ation | Negate RTS or | Assert RTS or send Xon |  |

|----------|----------|----------------|-------|---------------|------------------------|--|

|          |          | RX             | TX    | send Xoff     |                        |  |

| 00       | 00       | 8              | 16    | 8             | 0                      |  |

| 01       | 01       | 16             | 8     | 16            | 7                      |  |

| 10       | 10       | 24             | 24    | 24            | 15                     |  |

| 11       | 11       | 28             | 30    | 28            | 23                     |  |

## 6.4.2 128-byte FIFO mode

When either TXINTLVL, RXINTLVL, FLWCNTH or FLWCNTL in the 'first extra feature register set' contains any value other than 0x00, the transmit and receive trigger levels are set by TXINTLVL and RXINTLVL registers. TXINTLVL sets the trigger levels for the transmit FIFO, and the transmit trigger levels can be set to any value between 1 and 128 with granularity of 1. RXINTLVL sets the trigger levels for the receive FIFO, the receive trigger levels can be set to any value between 1 and 128 with granularity of 1.

When the effective FIFO size changes (that is, when FCR[0] toggles or when the combined content of TXINTLVL, RXINTLVL, FLWCNTH and FLWCNTL changes between equal and unequal to 0x00), both RX FIFO and TX FIFO will be reset (data in the FIFO will be lost).

#### 1.8 V single UART with 128-byte FIFOs and IrDA encoder/decoder

### 6.5 Hardware flow control

When automatic hardware flow control is enabled, the SC16C850L monitors the  $\overline{\text{CTS}}$  pin for a remote buffer overflow indication and controls the  $\overline{\text{RTS}}$  pin for local buffer overflows. Automatic hardware flow control is selected by setting EFR[6] (RTS) and EFR[7] (CTS) to a logic 1. If  $\overline{\text{CTS}}$  transitions from a logic 0 to a logic 1 indicating a flow control request, ISR[5] will be set to a logic 1 (if enabled via IER[7:6]), and the SC16C850L will suspend TX transmissions as soon as the stop bit of the character in process is shifted out. Transmission is resumed after the  $\overline{\text{CTS}}$  input returns to a logic 0, indicating more data may be sent.

When AFCR1[2] is set to logic 1 then the function of  $\overline{CTS}$  pin is mapped to the  $\overline{DSR}$  pin, and the function of  $\overline{RTS}$  is mapped to  $\overline{DTR}$  pin.  $\overline{DSR}$  and  $\overline{DTR}$  pins will behave as described above for  $\overline{CTS}$  and  $\overline{RTS}$ .

With the automatic hardware flow control function enabled, an interrupt is generated when the receive FIFO reaches the programmed trigger level. The  $\overline{RTS}$  (or  $\overline{DTR}$ ) pin will not be forced to a logic 1 (RTS off), until the receive FIFO reaches the next trigger level. However, the  $\overline{RTS}$  (or  $\overline{DTR}$ ) pin will return to a logic 0 after the receive buffer (FIFO) is unloaded to the next trigger level below the programmed trigger level. Under the above described conditions, the SC16C850L will continue to accept data until the receive FIFO is full.

When the TXINTLVL, RXINTLVL, FLWCNTH and FLWCNTL in the 'first extra feature register set' are all zeroes, the hardware and software flow control trigger levels are set by FCR[7:4]; see Table 6.

When the TXINTLVL, RXINTLVL, FLWCNTH or FLWCNTL in the 'first extra feature register set' contain any value other than 0x00, the hardware and software flow control trigger levels are set by FLWCNTH and FLWCNTL. The content in FLWCNTH determines how many bytes are in the receive FIFO before  $\overline{\text{RTS}}$  (or  $\overline{\text{DTR}}$ ) is de-asserted or Xoff is sent. The content in FLWCNTL determines how many bytes are in the receive FIFO before  $\overline{\text{RTS}}$  (or  $\overline{\text{DTR}}$ ) is asserted, or Xon is sent.

In 128-byte FIFO mode, hardware and software flow control trigger levels can be set to any value between 1 and 128 in granularity of 1. The value of FLWCNTH should always be greater than FLWCNTL. The UART does not check for this condition automatically, and if this condition is not met, spurious operation of the device might occur. When using FLWCNTH and FLWCNTL, these registers must be initialized to proper values before hardware or software flow control is enabled via the EFR register.

#### 6.6 Software flow control

When software flow control is enabled, the SC16C850L compares one or two sequentially received data characters with the programmed Xon or Xoff character value(s). If the received character(s) match the programmed Xoff values, the SC16C850L will halt transmission (TX) as soon as the current character(s) has completed transmission. When a match occurs, ISR bit 4 will be set (if enabled via IER[5]) and the interrupt output pin (if receive interrupt is enabled) will be activated. Following a suspension due to a match of the Xoff characters' values, the SC16C850L will monitor the receive data stream for a match to the Xon1/Xon2 character value(s). If a match is found, the SC16C850L will resume operation and clear the flags (ISR[4]).

SC16C850L **NXP Semiconductors**

#### 1.8 V single UART with 128-byte FIFOs and IrDA encoder/decoder

Reset initially sets the contents of the Xon/Xoff 8-bit flow control registers to a logic 0. Following reset, the user can write any Xon/Xoff value desired for software flow control. Different conditions can be set to detect Xon/Xoff characters and suspend/resume transmissions (see Table 24). When double 8-bit Xon/Xoff characters are selected, the SC16C850L compares two consecutive receive characters with two software flow control 8-bit values (Xon1, Xon2, Xoff1, Xoff2) and controls TX transmissions accordingly. Under the above described flow control mechanisms, flow control characters are not placed (stacked) in the receive FIFO. When using software flow control, the Xon/Xoff characters cannot be used for data transfer.

In the event that the receive buffer is overfilling, the SC16C850L automatically sends an Xoff character (when enabled) via the serial TX output to the remote UART. The SC16C850L sends the Xoff1/Xoff2 characters as soon as the number of received data in the receive FIFO passes the programmed trigger level. To clear this condition, the SC16C850L will transmit the programmed Xon1/Xon2 characters as soon as the number of characters in the receive FIFO drops below the programmed trigger level.

## 6.7 Special character detect

A special character detect feature is provided to detect an 8-bit character when EFR[5] is set. When an 8-bit character is detected, it will be placed on the user-accessible data stack along with normal incoming RX data. This condition is selected in conjunction with EFR[3:0] (see Table 24). Note that software flow control should be turned off when using this special mode by setting EFR[3:0] to all zeroes.

The SC16C850L compares each incoming receive character with Xoff2 data. If a match occurs, the received data will be transferred to the FIFO, and ISR[4] will be set to indicate detection of a special character. Although Table 8 "SC16C850L internal registers" shows Xon1, Xon2, Xoff1, Xoff2 with eight bits of character information, the actual number of bits is dependent on the programmed word length. Line Control Register bits LCR[1:0] define the number of character bits, that is, either 5 bits, 6 bits, 7 bits or 8 bits. The word length selected by LCR[1:0] also determines the number of bits that will be used for the special character comparison. Bit 0 in Xon1, Xon2, Xoff1, Xoff2 corresponds with the LSB bit for the received character.

## 6.8 Interrupt priority and time-out interrupts

The interrupts are enabled by IER[7:0]. Care must be taken when handling these interrupts. Following a reset, if Interrupt Enable Register (IER) bit 1 = 1, the SC16C850L will issue a Transmit Holding Register interrupt. This interrupt must be serviced prior to continuing operations. The ISR indicates the current singular highest priority interrupt only. A condition can exist where a higher priority interrupt masks the lower priority interrupt(s) (see Table 13). Only after servicing the higher pending interrupt will the lower priority interrupt(s) be reflected in the status register. Servicing the interrupt without investigating further interrupt conditions can result in data errors.

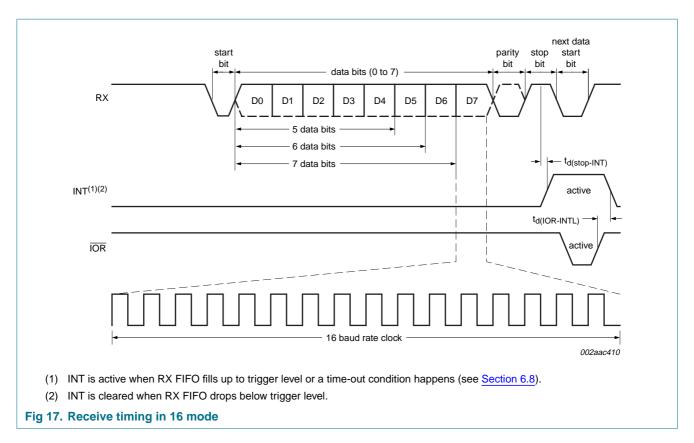

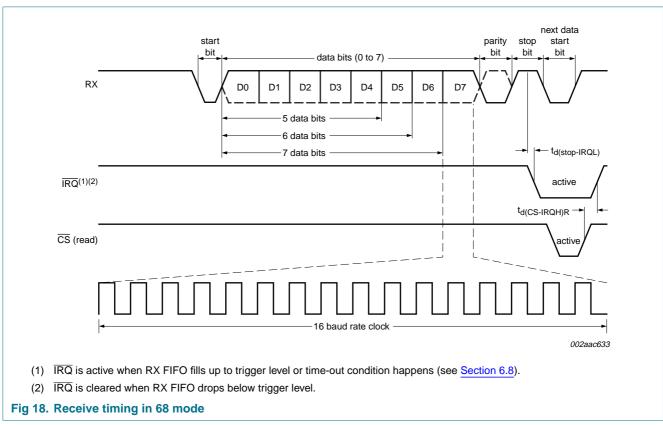

Receive Data Ready and Receive Time-Out have the same interrupt priority (when enabled by IER[0]), and it is important to serve these interrupts correctly. The receiver issues an interrupt after the number of characters have reached the programmed trigger level. In this case, the SC16C850L FIFO may hold more characters than the programmed trigger level. Following the removal of a data byte, the user should re-check LSR[0] to see if there are any additional characters. A Receive Time-Out will not occur if the receive FIFO is empty. The time-out counter is reset at the center of each stop bit received or

#### 1.8 V single UART with 128-byte FIFOs and IrDA encoder/decoder

each time the Receive Holding Register (RHR) is read. The actual time-out value is 4 character time, including data information length, start bit, parity bit, and the size of stop bit, that is,  $1 \times 1.5 \times 1.5$

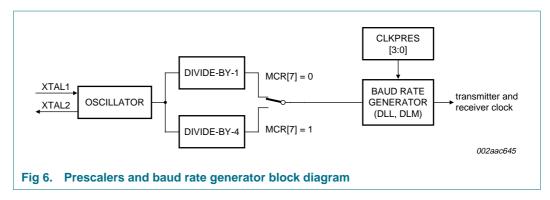

## 6.9 Programmable baud rate generator

The SC16C850L UART contains a programmable rational baud rate generator that takes any clock input and divides it by a divisor in the range between 1 and  $(2^{16} - 1)$ . The SC16C850L offers the capability of dividing the input frequency by rational divisor. The fractional part of the divisor is controlled by the CLKPRES register in the 'first extra feature register set'.

band rate =

$$\frac{f_{XTAL1}}{MCR[7] \times \left[16 \times \left(N + \frac{M}{16}\right)\right]}$$

(1)

where:

N is the integer part of the divisor in DLL and DLM registers;

M is the fractional part of the divisor in CLKPRES register;

f<sub>XTAL1</sub> is the clock frequency at XTAL1 pin.

Prescaler = 1 when MCR[7] is set to 0.

Prescaler = 4 when MCR[7] is set to 1.

A single baud rate generator is provided for the transmitter and receiver. The programmable Baud Rate Generator is capable of operating with a frequency of up to 80 MHz. To obtain maximum data rate, it is necessary to use full rail swing on the clock input. The SC16C850L can be configured for internal or external clock operation. For internal clock operation, an industry standard crystal is connected externally between the XTAL1 and XTAL2 pins (see Figure 7). Alternatively, an external clock can be connected to the XTAL1 pin (see Figure 8) to clock the internal baud rate generator for standard or custom rates (see Table 7).

The generator divides the input  $16 \times$  clock by any divisor from 1 to  $(2^{16} - 1)$ . The SC16C850L divides the basic external clock by 16. The baud rate is configured via the CLKPRES, DLL and DLM internal register functions. Customized baud rates can be achieved by selecting the proper divisor values for the MSB and LSB sections of the baud rate generator.

## 1.8 V single UART with 128-byte FIFOs and IrDA encoder/decoder

Programming the baud rate generator registers CLKPRES, DLM (MSB) and DLL (LSB) provides a user capability for selecting the desired final baud rate. The example in <u>Table 7</u> shows the selectable baud rate table available when using a 1.8432 MHz external clock input when MCR[7] = 0, and CLKPRES = 0x00.

Table 7. Baud rate generator programming table using a 1.8432 MHz clock when MCR[7] = 0 and CLKPRES[3:0] = 0

| Output baud rate (bit/s) | Output<br>16× clock divisor<br>(decimal) | Output<br>16× clock divisor<br>(hexadecimal) | DLM<br>program value<br>(hexadecimal) | DLL<br>program value<br>(hexadecimal) |

|--------------------------|------------------------------------------|----------------------------------------------|---------------------------------------|---------------------------------------|

| 50                       | 2304                                     | 900                                          | 09                                    | 00                                    |

| 75                       | 1536                                     | 600                                          | 06                                    | 00                                    |

| 110                      | 1047                                     | 417                                          | 04                                    | 17                                    |

| 150                      | 768                                      | 300                                          | 03                                    | 00                                    |

| 300                      | 384                                      | 180                                          | 01                                    | 80                                    |

| 600                      | 192                                      | C0                                           | 00                                    | C0                                    |

| 1.2 k                    | 96                                       | 60                                           | 00                                    | 60                                    |

| 2.4 k                    | 48                                       | 30                                           | 00                                    | 30                                    |

| 3.6 k                    | 32                                       | 20                                           | 00                                    | 20                                    |

| 4.8 k                    | 24                                       | 18                                           | 00                                    | 18                                    |

| 7.2 k                    | 16                                       | 10                                           | 00                                    | 10                                    |

| 9.6 k                    | 12                                       | 0C                                           | 00                                    | 0C                                    |

| 19.2 k                   | 6                                        | 06                                           | 00                                    | 06                                    |

## 1.8 V single UART with 128-byte FIFOs and IrDA encoder/decoder

Table 7. Baud rate generator programming table using a 1.8432 MHz clock when MCR[7] = 0 and CLKPRES[3:0] = 0 ...continued

| Output<br>baud rate<br>(bit/s) | Output<br>16× clock divisor<br>(decimal) | Output<br>16× clock divisor<br>(hexadecimal) | DLM<br>program value<br>(hexadecimal) | DLL<br>program value<br>(hexadecimal) |

|--------------------------------|------------------------------------------|----------------------------------------------|---------------------------------------|---------------------------------------|

| 38.4 k                         | 3                                        | 03                                           | 00                                    | 03                                    |

| 57.6 k                         | 2                                        | 02                                           | 00                                    | 02                                    |

| 115.2 k                        | 1                                        | 01                                           | 00                                    | 01                                    |

## 6.10 Loopback mode

The internal loopback capability allows on-board diagnostics. In the Loopback mode, the normal modem interface pins are disconnected and reconfigured for loopback internally (see Figure 9). MCR[3:0] register bits are used for controlling loopback diagnostic testing. In the Loopback mode, the transmitter output (TX) and the receiver input (RX) are disconnected from their associated interface pins, and instead are connected together internally. The  $\overline{\text{CTS}}$ ,  $\overline{\text{DSR}}$ ,  $\overline{\text{CD}}$ , and  $\overline{\text{RI}}$  are disconnected from their normal modem control input pins, and instead are connected internally to  $\overline{\text{RTS}}$ ,  $\overline{\text{DTR}}$ , MCR[3] ( $\overline{\text{OP2}}$ ) and MCR[2] ( $\overline{\text{OP1}}$ ). Loopback test data is entered into the transmit holding register via the user data bus interface, D[7:0]. The transmit UART serializes the data and passes the serial data to the receive UART via the internal loopback connection. The receive UART converts the serial data back into parallel data that is then made available at the user data interface D[7:0]. The user optionally compares the received data to the initial transmitted data for verifying error-free operation of the UART TX/RX circuits.

In this mode, the interrupt pin is 3-stated, therefore, the software must use the polling method (see Section 7.2.2) to send and receive data.

## 1.8 V single UART with 128-byte FIFOs and IrDA encoder/decoder

### 1.8 V single UART with 128-byte FIFOs and IrDA encoder/decoder

## 6.11 Sleep mode

Sleep mode is an enhanced feature of the SC16C850L UART. It is enabled when EFR[4], the enhanced functions bit, is set **and** when IER[4] bit is set.

#### 6.11.1 Conditions to enter Sleep mode

Sleep mode is entered when:

- · Modem input pins are not toggling.

- The serial data input line, RX, is idle for 4 character time (logic HIGH) and AFCR1[4] is logic 0. When AFCR1[4] is logic 1 the device will go to sleep regardless of the state of the RX pin (see Section 7.21 for the description of AFCR1 bit 4).

- The TX FIFO and TX shift register are empty.

- There are no interrupts pending.

- The RX FIFO is empty.

In Sleep mode, the UART clock and baud rate clock are stopped. Since most registers are clocked using these clocks, the power consumption is greatly reduced.

**Remark:** Writing to the divisor latches, DLL and DLM, to set the baud clock, must not be done during Sleep mode. Therefore, it is advisable to disable Sleep mode using IER[4] before writing to DLL or DLM.

## 6.11.2 Conditions to resume normal operation

SC16C850L resumes normal operation by any of the following:

- Receives a start bit on RX pin.

- Data is loaded into transmit FIFO.

- · A change of state on any of the modem input pins

If the device is awakened by one of the conditions described above, it will return to the Sleep mode automatically after all the conditions described in <u>Section 6.11.1</u> are met. The device will stay in Sleep mode until it is disabled by setting any channel's IER bit 4 to a logic 0.

When the SC16C850L is in Sleep mode and the host data bus (D[7:0], A[2:0],  $\overline{ION}$ ,  $\overline{ION}$ ,  $\overline{ION}$ ) remains in steady state, either HIGH or LOW, the Sleep mode supply current will be in the  $\mu A$  range as specified in <u>Table 36 "Static characteristics"</u>. If any of these signals is toggling or floating then the sleep current will be higher.

#### 6.12 Low power feature

A Low power feature is provided by the SC16C850L to prevent the switching of the host data bus from influencing the sleep current. When the pin LOWPWR is activated (logic HIGH), the device immediately and unconditionally goes into Low power mode. All clocks are stopped and most host interface pins are isolated to reduce power consumption. The device only returns to normal mode when the LOWPWR pin is de-asserted. The pin can be left unconnected because it has an internal pull-down resistor.

### 1.8 V single UART with 128-byte FIFOs and IrDA encoder/decoder

## **6.13 RS-485 features**

## 6.13.1 Auto RS-485 RTS control

Normally the  $\overline{RTS}$  pin is controlled by MCR[1], or if hardware flow control is enabled, the logic state of the  $\overline{RTS}$  pin is controlled by the hardware flow control circuitry. AFCR2[4] will take the precedence over the other two modes; once this bit is set, the transmitter will control the state of the  $\overline{RTS}$  pin. The transmitter automatically asserts the  $\overline{RTS}$  pin (logic 0) once the host writes data to the transmit FIFO, and de-asserts  $\overline{RTS}$  pin (logic 1) once the last bit of the data has been transmitted.

To use the auto RS-485 RTS mode the software would have to disable the hardware flow control function.

### 6.13.2 RS-485 RTS inversion

AFCR2[5] reverses the polarity of the  $\overline{RTS}$  pin if the UART is in auto RS-485  $\overline{RTS}$  mode.

When the transmitter has data to be sent it will de-asserts the  $\overline{RTS}$  pin (logic 1), and when the last bit of the data has been sent out the transmitter asserts the  $\overline{RTS}$  pin (logic 0).

### 6.13.3 Auto 9-bit mode (RS-485)

AFCR2[0] is used to enable the 9-bit mode (Multi-drop or RS-485 mode). In this mode of operation, a 'master' station transmits an address character followed by data characters for the addressed 'slave' stations. The slave stations examine the received data and interrupt the controller if the received character is an address character (parity bit = 1).

To use the automatic 9-bit mode, the software would have to disable the hardware and software flow control functions.

#### 6.13.3.1 Normal Multi-drop mode

The 9-bit Mode in AFCR2[0] is enabled, but not Special Character Detect (EFR[5]). The receiver is set to Force Parity 0 (LCR[5:3] = 111) in order to detect address bytes.

With the receiver initially disabled, it ignores all the data bytes (parity bit = 0) until an address byte is received (parity bit = 1). This address byte will cause the UART to set the parity error. The UART will generate a line status interrupt (IER[2] must be set to '1' at this time), and at the same time puts this address byte in the RX FIFO. After the controller examines the byte it must make a decision whether or not to enable the receiver; it should enable the receiver if the address byte addresses its ID address, and must not enable the receiver if the address byte does not address its ID address.

If the controller enables the receiver, the receiver will receive the subsequent data until being disabled by the controller after the controller has received a complete message from the 'master' station. If the controller does not disable the receiver after receiving a message from the 'master' station, the receiver will generate a parity error upon receiving another address byte. The controller then determines if the address byte addresses its ID address, if it is not, the controller then can disable the receiver. If the address byte addresses the 'slave' ID address, the controller takes no further action, and the receiver will receive the subsequent data.

#### 1.8 V single UART with 128-byte FIFOs and IrDA encoder/decoder

#### 6.13.3.2 Auto address detection

If Special Character Detect is enabled (EFR[5] is set and the Xoff2 register contains the address byte) the receiver will try to detect an address byte that matches the programmed character in the Xoff2 register. If the received byte is a data byte or an address byte that does not match the programmed character in the Xoff2 register, the receiver will discard these data. Upon receiving an address byte that matches the Xoff2 character, the receiver will be automatically enabled if not already enabled, and the address character is pushed into the RX FIFO along with the parity bit (in place of the parity error bit). The receiver also generates a line status interrupt (IER[2] must be set to '1' at this time). The receiver will then receive the subsequent data from the 'master' station until being disabled by the controller after having received a message from the 'master' station.

If another address byte is received and this address byte does not match the Xoff2 character, the receiver will be automatically disabled and the address byte is ignored. If the address byte matches the Xoff2 character, the receiver will put this byte in the RX FIFO along with the parity bit in the parity error bit (LSR bit 2).

## 7. Register descriptions

<u>Table 8</u> details the assigned bit functions for the SC16C850L internal registers. The assigned bit functions are more fully defined in <u>Section 7.1</u> through <u>Section 7.23</u>.

**NXP Semiconductors**

Table 8. SC16C850L internal registers

| A2  | <b>A1</b> | A0    | Register       | Default[1] | Bit 7                          | Bit 6                    | Bit 5                 | Bit 4                        | Bit 3                        | Bit 2                               | Bit 1                                        | Bit 0                                       | R/W |

|-----|-----------|-------|----------------|------------|--------------------------------|--------------------------|-----------------------|------------------------------|------------------------------|-------------------------------------|----------------------------------------------|---------------------------------------------|-----|

| Ger | eral      | regi  | ster set[2]    |            |                                |                          |                       |                              |                              |                                     |                                              |                                             |     |

| 0   | 0         | 0     | RHR            | XX         | bit 7                          | bit 6                    | bit 5                 | bit 4                        | bit 3                        | bit 2                               | bit 1                                        | bit 0                                       | R   |

| 0   | 0         | 0     | THR            | XX         | bit 7                          | bit 6                    | bit 5                 | bit 4                        | bit 3                        | bit 2                               | bit 1                                        | bit 0                                       | W   |

| 0   | 0         | 1     | IER            | 00         | CTS interrupt[3]               | RTS interrupt[3]         | Xoff interrupt[3]     | Sleep<br>mode <sup>[3]</sup> | modem<br>status<br>interrupt | receive line<br>status<br>interrupt | transmit<br>holding<br>register<br>interrupt | receive<br>holding<br>register<br>interrupt | R/W |

| 0   | 1         | 0     | FCR            | 00         | RCVR<br>trigger<br>(MSB)       | RCVR<br>trigger<br>(LSB) | TX trigger (MSB)[3]   | TX trigger (LSB)[3]          | reserved                     | XMIT FIFO reset                     | RCVR FIFO reset                              | FIFOs<br>enable                             | W   |

| 0   | 1         | 0     | ISR            | 01         | FIFOs<br>enabled               | FIFOs<br>enabled         | INT priority<br>bit 4 | INT priority bit 3           | INT priority<br>bit 2        | INT priority<br>bit 1               | INT priority<br>bit 0                        | INT status                                  | R   |

| 0   | 1         | 1     | LCR            | 00         | divisor latch enable           | set break                | set parity            | even parity                  | parity<br>enable             | stop bits                           | word length<br>bit 1                         | word length<br>bit 0                        | R/W |

| 1   | 0         | 0     | MCR            | 00         | clock<br>select <sup>[3]</sup> | IrDA enable              | INT type              | loopback                     | OP2                          | OP1                                 | RTS                                          | DTR                                         | R/W |

| 1   | 0         | 1     | LSR            | 60         | FIFO data error                | THR and TSR empty        | THR empty             | break<br>interrupt           | framing error                | parity error                        | overrun<br>error                             | receive data ready                          | R   |

| 1   | 0         | 1     | EFCR           | 00         | reserved                       | reserved                 | reserved              | reserved                     | reserved                     | Enable extra feature bit 1          | Enable extra feature bit 0                   | Enable<br>TXLVLCNT/<br>RXLVLCNT             | W   |

| 1   | 1         | 0     | MSR            | X0         | CD                             | RI                       | DSR                   | CTS                          | $\Delta \overline{CD}$       | $\Delta \overline{RI}$              | $\Delta \overline{DSR}$                      | $\Delta \overline{CTS}$                     | R   |

| 1   | 1         | 1     | SPR            | FF         | bit 7                          | bit 6                    | bit 5                 | bit 4                        | bit 3                        | bit 2                               | bit 1                                        | bit 0                                       | R/W |

| Spe | cial      | regis | ster set[4]    |            |                                |                          |                       |                              |                              |                                     |                                              |                                             |     |

| 0   | 0         | 0     | DLL            | XX         | bit 7                          | bit 6                    | bit 5                 | bit 4                        | bit 3                        | bit 2                               | bit 1                                        | bit 0                                       | R/W |

| 0   | 0         | 1     | DLM            | XX         | bit 15                         | bit 14                   | bit 13                | bit 12                       | bit 11                       | bit 10                              | bit 9                                        | bit 8                                       | R/W |

| Sec | ond       | spec  | ial register s | et[6]      |                                |                          |                       |                              |                              |                                     |                                              |                                             |     |

| 0   | 1         | 1     | TXLVLCNT       | 00         | bit 7                          | bit 6                    | bit 5                 | bit 4                        | bit 3                        | bit 2                               | bit 1                                        | bit 0                                       | R   |

| 1   | 0         | 0     | RXLVLCNT       | 00         | bit 7                          | bit 6                    | bit 5                 | bit 4                        | bit 3                        | bit 2                               | bit 1                                        | bit 0                                       | R   |

V single UART with 128-byte FIFOs and IrDA encoder/decoder

NXP

Semiconductors

| 2 | Table 8. | SC16C850L | internal | registers | continued |

|---|----------|-----------|----------|-----------|-----------|

|---|----------|-----------|----------|-----------|-----------|

|           |            |       | 010000E III    |             |          |          |                                |                                                           |                          |                                 |                          |                          |     |

|-----------|------------|-------|----------------|-------------|----------|----------|--------------------------------|-----------------------------------------------------------|--------------------------|---------------------------------|--------------------------|--------------------------|-----|

| <b>A2</b> | <b>A</b> 1 | A0    | Register       | Default[1]  | Bit 7    | Bit 6    | Bit 5                          | Bit 4                                                     | Bit 3                    | Bit 2                           | Bit 1                    | Bit 0                    | R/W |

| Enh       | nance      | ed fe | ature registe  | r set[5]    |          |          |                                |                                                           |                          |                                 |                          |                          |     |

| 0         | 1          | 0     | EFR            | 00          | Auto CTS | Auto RTS | special<br>character<br>select | Enable<br>IER[7:4],<br>ISR[5:4],<br>FCR[5:4],<br>MCR[7:5] | Cont-3 TX,<br>RX Control | Cont-2 TX,<br>RX Control        | Cont-1 TX,<br>RX Control | Cont-0 TX,<br>RX Control | R/W |

| 1         | 0          | 0     | Xon1           | 00          | bit 7    | bit 6    | bit 5                          | bit 4                                                     | bit 3                    | bit 2                           | bit 1                    | bit 0                    | R/W |

| 1         | 0          | 1     | Xon2           | 00          | bit 15   | bit 14   | bit 13                         | bit 12                                                    | bit 11                   | bit 10                          | bit 9                    | bit 8                    | R/W |

| 1         | 1          | 0     | Xoff1          | 00          | bit 7    | bit 6    | bit 5                          | bit 4                                                     | bit 3                    | bit 2                           | bit 1                    | bit 0                    | R/W |

| 1         | 1          | 1     | Xoff2          | 00          | bit 15   | bit 14   | bit 13                         | bit 12                                                    | bit 11                   | bit 10                          | bit 9                    | bit 8                    | R/W |

| Firs      | st ext     | ra fe | ature registe  | r set[7]    |          |          |                                |                                                           |                          |                                 |                          |                          |     |

| 0         | 1          | 0     | TXINTLVL       | 0x00        | bit 7    | bit 6    | bit 5                          | bit 4                                                     | bit 3                    | bit 2                           | bit 1                    | bit 0                    | R/W |

| 1         | 0          | 0     | RXINTLVL       | 0x00        | bit 7    | bit 6    | bit 5                          | bit 4                                                     | bit 3                    | bit 2                           | bit 1                    | bit 0                    | R/W |

| 1         | 1          | 0     | FLWCNTH        | 0x00        | bit 7    | bit 6    | bit 5                          | bit 4                                                     | bit 3                    | bit 2                           | bit 1                    | bit 0                    | R/W |

| 1         | 1          | 1     | FLWCNTL        | 0x00        | bit 7    | bit 6    | bit 5                          | bit 4                                                     | bit 3                    | bit 2                           | bit 1                    | bit 0                    | R/W |

| Sec       | ond        | extra | a feature regi | ster set[8] |          |          |                                |                                                           |                          |                                 |                          |                          |     |

| 0         | 1          | 0     | CLKPRES        |             | reserved | reserved | reserved                       | reserved                                                  | bit 3                    | bit 2                           | bit 1                    | bit 0                    | R/W |

| 1         | 0          | 0     | RS485TIME      | 0x00        | bit 7    | bit 6    | bit 5                          | bit 4                                                     | bit 3                    | bit 2                           | bit 1                    | bit 0                    | R/W |

| 1         | 1          | 0     | AFCR2          | 0x00        | reserved | reserved | RS485 RTS<br>Invert            | Auto RS485<br>RTS                                         | RS485<br>RTS/DTR         | Transmitter<br>Disable          | Receiver<br>Disable      | 9-bit Enable             | R/W |

| 1         | 1          | 1     | AFCR1          | 0x00        | reserved | reserved | reserved                       | Sleep<br>RXLow                                            | reserved                 | RTS/CTS<br>mapped to<br>DTR/DSR | Software<br>Reset        | TSR<br>Interrupt         | R/W |

- [1] The value shown represents the register's initialized HEX value; X = not applicable.

- [2] Accessible only when LCR[7] is logic 0, and EFCR[2:1] are logic 0.

- [3] This bit is only accessible when EFR[4] is set.

- [4] Baud rate registers accessible only when LCR[7] is logic 1.

- [5] Enhanced Feature Register, Xon1/Xon2 and Xoff1/Xoff2 are accessible only when LCR is set to 0xBF, and EFCR[2:1] are logic 0.

- [6] Second Special registers are accessible only when EFCR[0] = 1, and EFCR[2:1] are logic 0.

- [7] First extra feature register set is only accessible when EFCR[2:1] = 01b.

- [8] Second extra feature register set is only accessible when EFCR[2:1] = 10b.

#### 1.8 V single UART with 128-byte FIFOs and IrDA encoder/decoder

## 7.1 Transmit (THR) and Receive (RHR) Holding Registers